⏪Previous Next⏩

Let us begin with a simple illustration to explain the basic rationale behind interrupt mode of data transfer.

Suppose a program needs input from a device which communicates using interrupt.

Even with the present-day technology the devices are one thousand or more times slower than the processor.

So if the program waits on the input device it would cycle through many processor cycles just waiting for the input device to be ready to communicate.

This is where the interrupt mode of communication scores.

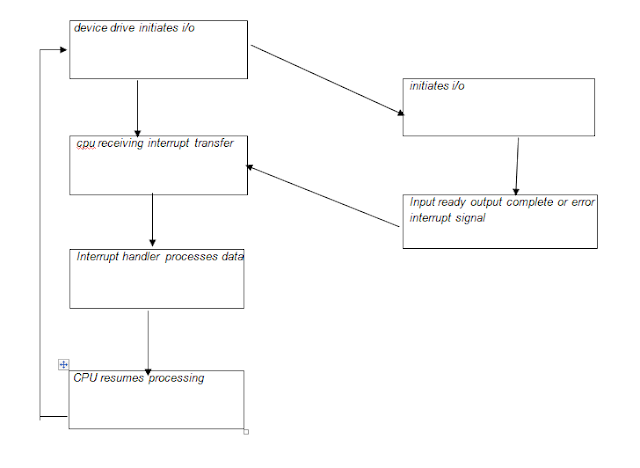

To begin with, a program may initiate IO request and advance without suspending its operation. At the time when the device is actually ready to establish an IO, the device raises an interrupt to seek communication.

Immediately the program execution is suspended temporarily and current state of the process is stored.

The control is passed on to an interrupt service routine (which may be specific to the device) to perform the desired input.

Subsequently, the suspended process context is restored to resume the program from the point of its suspension.

Internal Interrupt:

The source of interrupt may be a memory resident process or a function from within the processor. We regard such an interrupt as an internal

interrupt.

A processor malfunction results in an internal interrupt. An attempt to

divide by zero or execute an illegal or non-existent instruction code results in an

internal interrupt as well.

A malfunction arising from a division by zero is called a trap.

Internal interrupt may be caused by a timer as well.

This may be because either the allocated processor time slice to a process has elapsed or for some reason the process needs to be pre-empted. Note that an RTOS may pre-empt a running process by using an interrupt to ensure that the stipulated response time required is met. This would also be a case of internal interrupt.

External Interrupt:

If the source of interrupt in not internal, i.e. it is other than a

process or processor related event then it is an external interrupt.

This may be caused by a device which is seeking attention of a processor. As indicated earlier, a program may seek an IO and issue an IO command but proceed.

After a while, the device from which IO was sought is ready to communicate. In that case the device may raise an interrupt. This would be a case of an external interrupt.

Software Interrupt:

Most OSs offer two modes of operation, the user mode and

the system mode.

Whenever a user program makes a system call, be it for IO or a

special service, the operation must have a transition from user mode to system

mode.

An interrupt is raised to effect this transition from user to system mode of

operation. Such an interrupt is called a software interrupt.

We shall next examine how an interrupt is serviced. Suppose we are executing an instruction at i in program P when interrupt signal has been raised.

Let us also assume that we have an interrupt service routine which is to be initiated to service the interrupt.

The following steps describe how a typical interrupt service may happen.

DMA (Direct memory access)Mode of Data Transfer :

This is a mode of data transfer in which IO is performed in large data blocks.

For instance, the disks communicate in data blocks of sizes like 512 bytes or 1024 bytes.

The direct memory access, or DMA ensures access to main memory without processor intervention or support.

Such independence from processor makes this mode of transfer extremely efficient.

When a process initiates a direct memory access (DMA) transfer, its execution is briefly suspended (using an interrupt) to set up the DMA control.

The DMA control requires the information on starting address in main memory and size of data for transfer.

This information is stored in DMA controller. Following the DMA set up, the program resumes from the point of suspension.

The device communicates with main memory stealing memory access cycles in competition with other devices and processor of disk to main memory transfer in DMA mode.

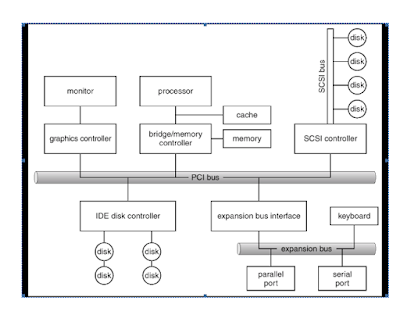

We first note that there is a disk controller to regulate communication from one or more disk drives.

This controller essentially isolates individual devices from direct communication with the CPU or main memory.

The communication is regulated to first happen between the device and the controller, and later between the controller and main memory or CPU if so needed. Note that these devices communicate in blocks of bits or bytes as a data stream. Clearly, an unbuffered communication is infeasible via the data bus.

The bus has its own timing control protocol.

. Once the controller buffer has the required data, then one can envisage to put the

controller in contention with CPU and main memory or CPU to obtain an access to the bus. Thus if the controller can get the bus then by using the address and data bus it can directly communicate with main memory.

This transfer shall be completely independent of program control from the processor memory.

i/o Hardware

IO management requires that a proper set-up is created by an application on computer system with an IO device.

An IO operation is a combination of HW and SW instructions as shown in Figure Following the issuance of an IO command, OS kernel resolves it, and then communicates

⏪Previous Next⏩

- What is an Operating System ?

- Discuss the structure off OS ?

- Explain type of OS?

- Explain Function of OS?

- Explain OS Services ?

- What do mean by system call ?List different type ofsystem call available ?

- what is process ? and Characteristics ?

- What is different process state? explain the same in details?

- write short note on user level and kernal level threads?

- explain what is thread and its type ?

- explain scheduler ? (short term,medium term,and long term)

- state and explain scheduling criteria ?

- Explain scheduling algorithm ? [ FCFS,SJF,PRIORITY,ROUND ROBINE.]

- What is process synchronization ? explain critical section problem and race condition ?

- what is Race Condition ?

- what is critical section problem?

- explain classical problem of synchronization?

- explain bounded - buffer problem?

- explain reader - writer problem ?

- explain Dining Philosophers Problem ?

- explain semaphores ? its type ?

- What is deadlock ?

- What are the 4 condition to produce deadlock ?

- explain methods of handling deadlock ?

- explain in detail deadlock prevention ?

- write short note on deadlock avoidance ?

- explain deadlock detection ?

- explain Banker algorithm with example ?

- What are memory management ?

- what is contiguous memory allocation and non - contiguous memory allocation ?

- explain concept of paging with neat diagram?

- differentiate contiguous and non - contiguous memory allocation ?

- explain in details various partitioning memory management?

- explain the concept of Segmentation ?

- what is Thrashing explain in details ?

0 Comments